# OpenVPX closes the integration gap between off-the-shelf VPX modules

By Jeff Porter

Until recently, widespread acceptance of VPX (VITA 46) suffered from the lack of a system-level interoperability specification. However, VPX systems integration just got a lot easier, thanks to OpenVPX (VITA 65).

With a module or board-level approach, the VPX (VITA 46) base specification and associated "dot specs" stop short of addressing system-level issues. Without any further definition, the VPX community was in jeopardy of fragmenting into a group of vendors with incompatible, standard-in-name-only products.

Fortunately, the VPX community united and created the OpenVPX (VITA 65) specification, paving the way toward cutting-edge VPX specifications within the rugged embedded marketplace. OpenVPX builds on the module-centric VPX specifications by providing a nomenclature for system integrators, module designers, and backplane providers to use when describing and defining aspects and characteristics of a system. OpenVPX accomplishes this via planes and profiles pertinent to the 3U and 6U form factors, providing a blend of interoperable flexibility for modern military VPX systems.

## Telecom lends its planes to OpenVPX

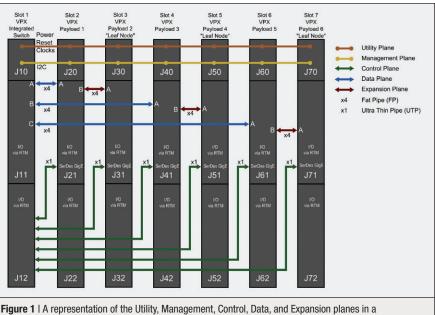

The term "plane" is common within telecom architectures such as AdvancedTCA and MicroTCA and serves the same purpose within OpenVPX: to help categorize requirements while not changing the physical design structure of VPX. Accordingly, five planes have been defined within OpenVPX: Utility, Management, Control, Data, and Expansion (Figure 1). A closer look at each plane will provide understanding.

#### Utility plane

The Utility Plane encompasses the power, clock, and reset connections within the system. OpenVPX has aided interoperability within the Utility Plane by clarifying reset requirements throughout the system as well as defining power profiles for modules and development chassis. Clarification of reset requirements and the definition of power profiles were fundamental roadblocks in system interoperability prior to OpenVPX.

#### Management Plane

The Management Plane defines a hardware and software framework for platform-level tasks such as health monitoring, inventory management, event logging, fault detection, and fault isolation. OpenVPX supports the ongoing efforts of VITA 46.11 in defining optional system management components at the payload module level (IPMCs) and the chassis level (ChMCs). For the first time within VPX, an industry-standard IPMIbased infrastructure is being defined for the collection and distribution of module sensor data. VITA 46.11, like OpenVPX, leverages from the AdvancedTCA and MicroTCA specifications while removing focus from telecom-specific features, such as hot swap, not required within the rugged embedded market.

#### **Control Plane**

The Control Plane defines a systemlevel communication path for control traffic. OpenVPX has focused on using the 1000BASE-BX SERDES GbE protocol for the Control Plane. This is especially beneficial with the real-estateconstrained and pin-limited 3U profiles, as the SERDES-based GbE protocol reduces the pin count by half and removes the requirement for large on-card magnetics. For many systems, the GbE Control Plane can also take the place of the longstanding VMEbus.

#### Data Plane

The Data Plane provides a high-throughput mechanism based on switched fabrics for transferring data between system peers. This can be accomplished by using a distributed architecture or utilizing a switch to provide a centralized location through which modules can route communications. With the standardization of the high-speed serial switched fabric Data Plane, OpenVPX provides the bandwidth and forward compatibility to support the data throughput requirements of both current and future applications.

#### **Expansion** Plane

The Expansion Plane presents a highthroughput mechanism for transferring

representative 3U OpenVPX backplane.

data, intended for sharing data between two specific entities within a system. The Expansion Plane provides a standard mechanism for implementing functions such as moving data to and from a coprocessor or off-load engine as well as moving data from a sensor interface module to a processor module.

### Profiles smooth multi-vendor module integration

Before OpenVPX's clearly defined standard for backplane fabric pinouts, integrating a system utilizing VPX modules from multiple vendors was often a costly and time-consuming effort. The newly defined OpenVPX profiles for the slot, module, switch, backplane, and development chassis ease system integration. OpenVPX defines *slot profiles* as the physical location and logical definition of the planes from the backplane's perspective, while *module profiles* define protocol requirements.

To accommodate flexibility of development systems, encourage innovation, and assist the future evolution of VPX, OpenVPX has identified a number of "User Defined I/O" regions within the module profiles. While the location of "User Defined I/O" on the connectors has been set by the module profiles, the specific allocation of these interfaces is characterized by the module vendor. This approach focuses the standard on inter-module fabric communication. Since access to these "out-of-the-box" I/O interfaces within development systems is provided with the use of a costeffective Rear Transition Module (RTM) or through front-panel connectors on the module itself, there is little advantage in specifying required I/O pinouts for modules within the development environment. Since the majority of deployed environments require the customization of the backplane to accommodate rugged box-level connectors, there is also no practical benefit to locking down user I/O pinouts for deployed systems.

OpenVPX also defines power and thermal profiles to provide chassis and module designers standard guidelines upon which to base designs. Realizing the system constraints and distribution (I2R) losses associated with the lower-voltage 5 V-based legacy systems, OpenVPX has taken the forward-looking stance of defining a higher-voltage 12 V-based power profile for 3U as well as 6U. Let's take a look at more OpenVPX profiles' advantages related to the 3U and 6U form factors specifically.

**3U OpenVPX Profiles: SWaP focused** Amidst the military's clamor for SWaPconstrained wares, OpenVPX defines the multipurpose 3U Payload Slot Profiles "SLT3-PAY-2F2U-14.2.3" and "SLT3-PAY-1F1F2U-14.2.4." These particular profiles maximize the configurability of the pin-constrained 3U module by leaving about one-third of P/J1 pins open as "user defined." This provides an excellent location to route mezzanine I/O or external I/O from the VPX module. While defining a number of separate profiles increases variability within the ecosystem, it also serves to provide flexible solutions for the system integrator. Additionally, the similarities between profiles allow module vendors to design a single module that can comply with multiple module profiles.

Another important achievement for OpenVPX is that for the first time within the VPX domain, standard switchbased profiles have been fully defined: a key requirement for the proliferation of high-speed switched fabrics such as PCI Express, GbE, and 10 GbE within VPX. Additionally, the integrated 3U switch slot "SLT3-SWH-6F6U-14.4.1" profile focuses on reducing system slot count and overall system SWaP by defining a single switch slot that performs the duties of both Data Plane and Control Plane switches. The integrated switch includes the capability of providing an external access point to the system via GbE or 10 GbE through the user-defined pins at the bottom of P/J2. If the integrated

# x86 Processor Boards for critical embedded applications

## Special

switch is also designed to accommodate a mezzanine, it provides a centralized location for the Data Plane Root Complex and Control Plane management. The Extreme Engineering Solutions (X-ES) XChange3012 (Figure 2) is an example of an OpenVPX 3U integrated switch.

In addition to the profiles discussed, yet another new concept for VPX brought forward by OpenVPX is a standardized storage module profile. The storage module profile "SLT3-STO-2U-14.5.1" provides VPX with a standardized 3U storage module pinout to enable the production of commodity VPX storage modules. This, in turn, helps reduce lead time and costs of this critical component within many systems.

#### 6U OpenVPX profiles surpass VME

For 6U VPX, OpenVPX has further advanced the performance capabilities over legacy 6U form factors such as VME and even CompactPCI. These advancements include defining P/J2 on 6U modules for something other than legacy VME support: Previous VPX specifications reserved P/J2 on 6U modules for VME, which limited the performance impact of VPX by tying up precious pins that could otherwise be used by high-speed

Figure 2 | The Extreme Engineering Solutions (X-ES) XChange3012 OpenVPX 3U integrated switch

differential I/O, but that is not the case with 6U OpenVPX. SERDES GbE is additionally defined as a Control Plane interface with 6U OpenVPX. By focusing on SERDES GbE as opposed to 1000BASE-T for the control plane interface, 6U systems that include a Control Plane switch will benefit from increased pin availability and more available board real estate through the removal of on-card magnetics.

The 6U payload profile "SLT6-PAY-4F1Q2U2T-10.2.1" is an example of a multipurpose 6U profile that utilizes the advantages of SERDES Control Plane ports, provides a large amount of userdefined I/O, and allocates P/J2 for highthroughput serial I/O. Another advantage of this particular profile is that a module designed in this profile can also be designed to comply with several other 6U OpenVPX payload and peripheral profiles.

## The right stuff: Interoperability and flexibility

OpenVPX does not take the "one-profilefits-all" approach that has limited innovation within other form factors. Instead, it addresses major interoperability issues while allowing for flexibility within the system, as enabled by its planes, backplane profiles, and flexible module profiles featuring user-defined I/O. **CS**

Jeff Porter is a Senior Systems Engineer at Extreme Engineering Solutions (X-ES). Jeff received his BS in Electrical and Computer Engineer-

ing from the University of Wisconsin, and has been an engineer at X-ES since its inception. He can be contacted at jporter@xes-inc.com.

Extreme Engineering Solutions 608-833-1155 www.xes-inc.com